#### SystemVerilog for VHDL Users

Tom Fitzpatrick

Principal Technical Specialist

Synopsys, Inc.

SYNOPSYS®

#### Agenda

- Introduction

- SystemVerilog Design Features

- SystemVerilog Assertions

- SystemVerilog Verification Features

- Using SystemVerilog and VHDL Together

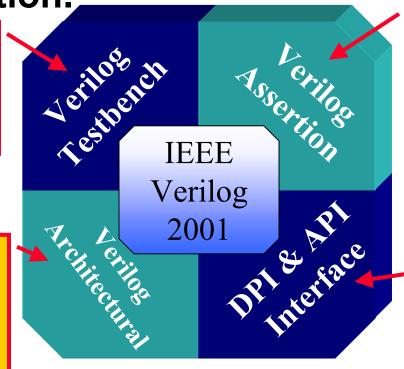

## SystemVerilog Charter

Charter: Extend Verilog IEEE 2001 to higher abstraction levels for Architectural and Algorithmic Design, and Advanced Verification.

Transaction-Level Full Testbench Language with Coverage

Design

Abstraction:

Interface

semantics, abstract

data types,

abstract operators

and expressions

Advanced

verification capability

for semiformal and

formal methods.

The Assertion

Language Standard

For Verilog

<u>Direct C</u> interface, <u>Assertion API</u> and <u>Coverage API</u>

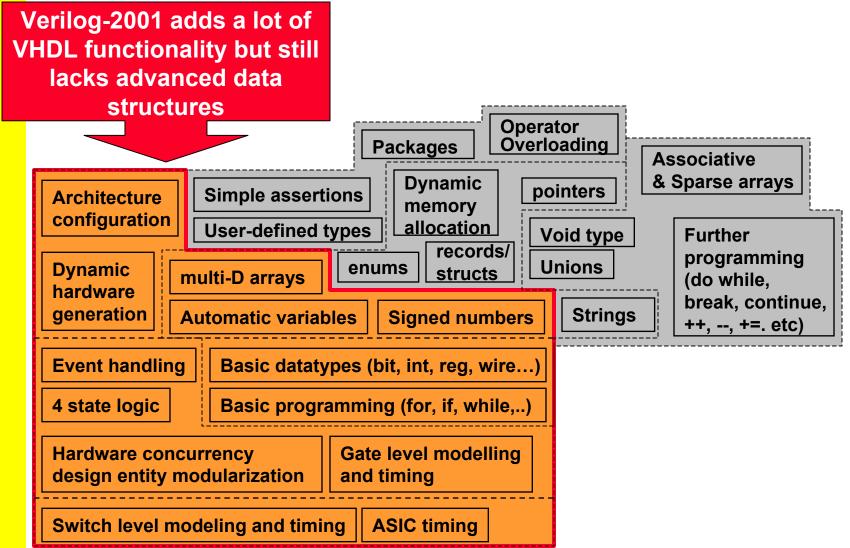

## SystemVerilog: Verilog 1995

Event handling Basic datatypes (bit, int, reg, wire...)

4 state logic Basic programming (for, if, while,..)

Hardware concurrency design entity modularization Gate level modelling and timing

Switch level modeling and timing ASIC timing

Verilog-95:

Single language

for design &

testbench

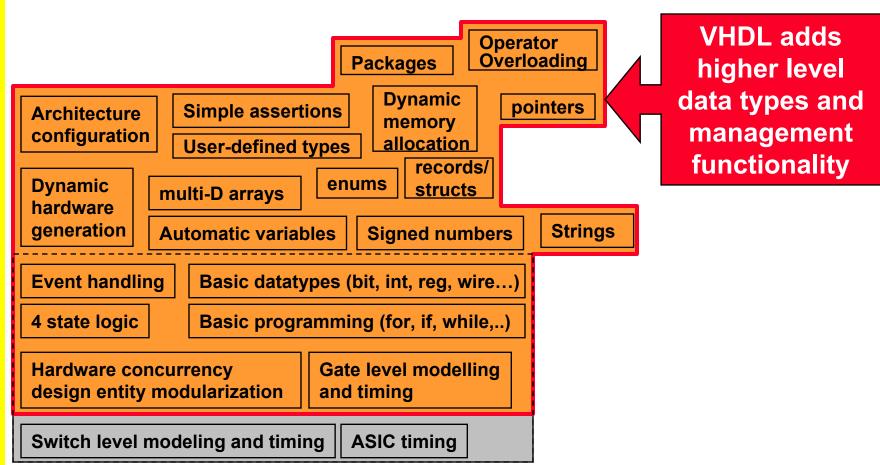

## SystemVerilog: VHDL

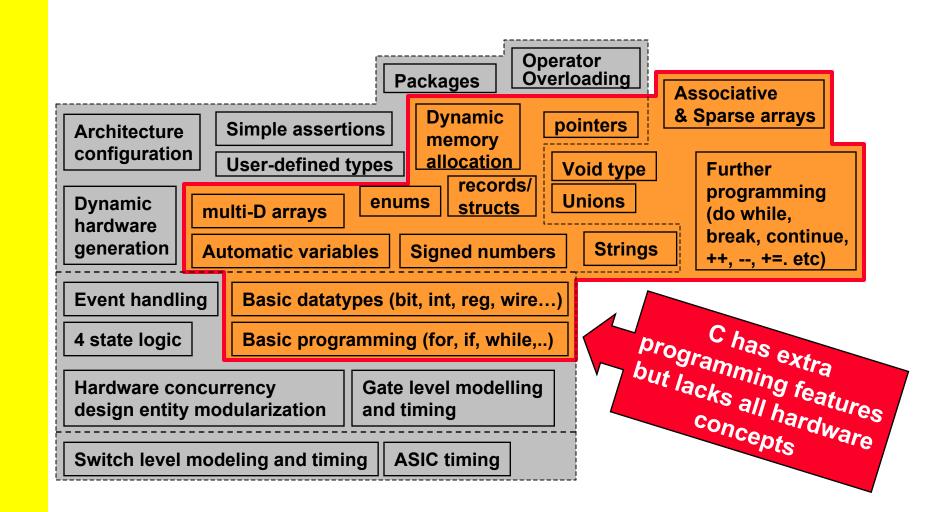

#### **Semantic Concepts: C**

## SystemVerilog: Verilog-2001

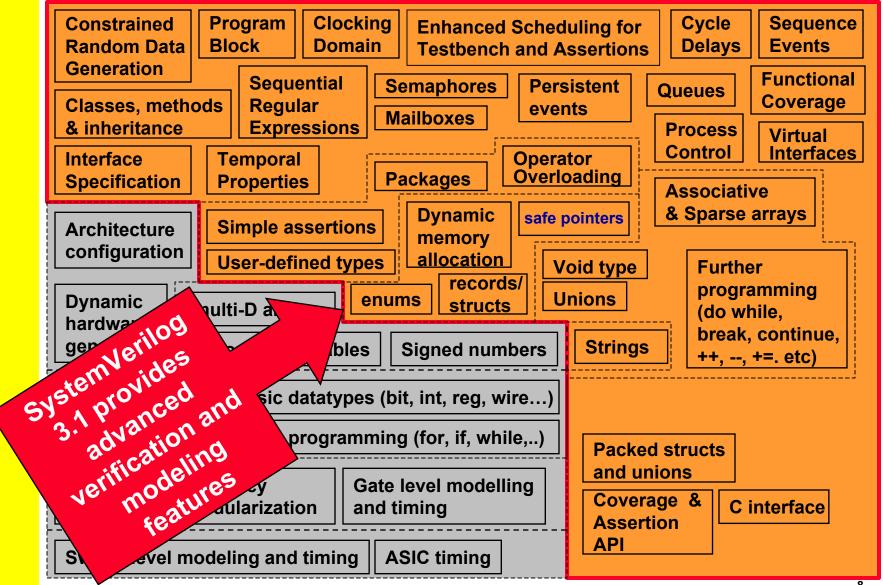

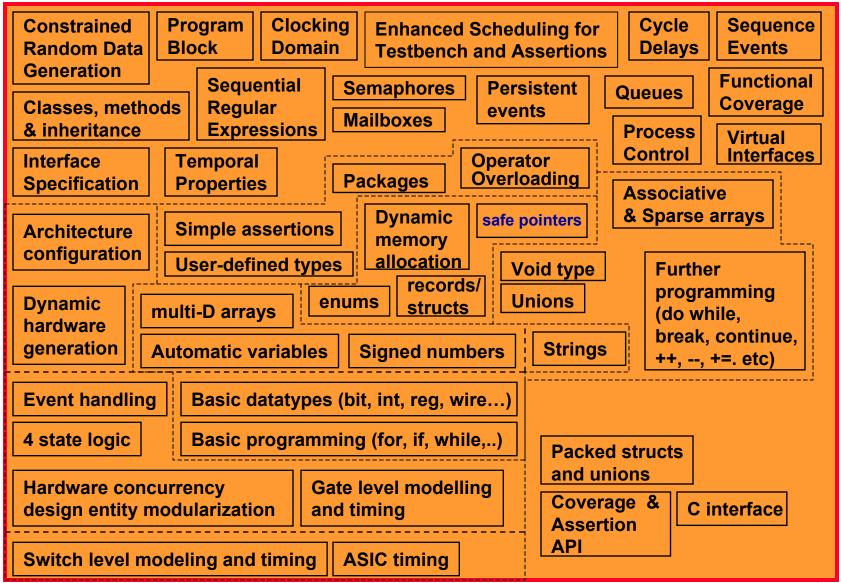

# SystemVerilog: Enhancements

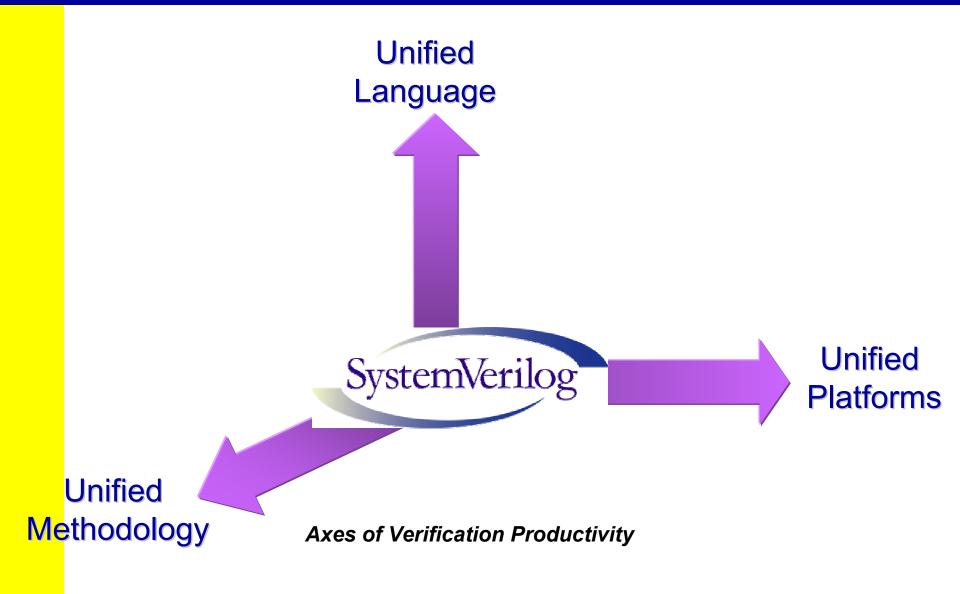

# SystemVerilog: Unified Language

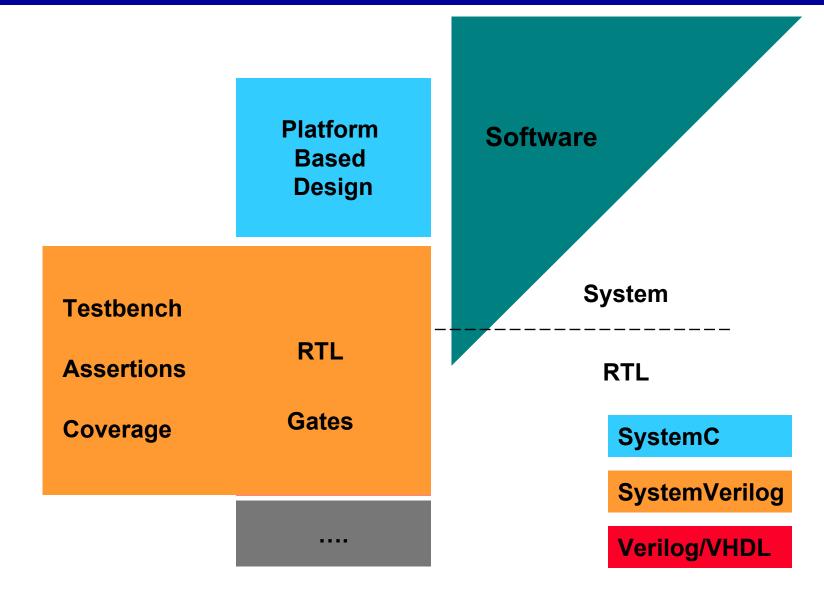

# SystemC & SystemVerilog

### Agenda

- Introduction

- SystemVerilog Design Features

- SystemVerilog Assertions

- SystemVerilog Verification Features

- Using SystemVerilog and VHDL Together

#### Basic SystemVerilog Data Types

```

reg r;  // 4-state Verilog-2001 single-bit datatype

integer i; // 4-state Verilog-2001 >= 32-bit datatype

bit b;  // single bit 0 or 1

logic w;  // 4-valued logic, x 0 1 or z as in Verilog

byte b8;  // 8 bit signed integer

int i;  // 2-state, 32-bit signed integer

```

**Explicit 2-state Variables Allow Compiler Optimizations to Improve Performance**

The unresolved type "logic" in SystemVerilog is equivalent to "std\_ulogic" in VHDL

#### Familiar C Features In SystemVerilog

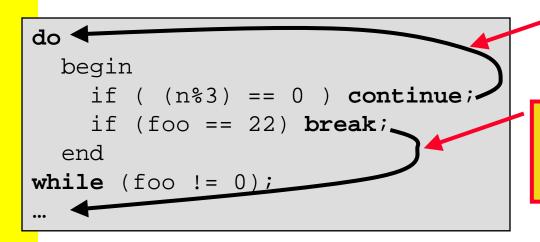

next loop iteration

break exits the loop (= "exit" in VHDL works with:

for

while

forever

repeat

do while

Blocking Assignments as expressions

```

if ((a=b)) ...

while ((a = b || c))

```

Extra parentheses required to distinguish from if(a==b)

Auto increment/ decrement operators

```

x++;

if (--c > 17) c=0;

```

#### SystemVerilog Struct = Record

```

type PKT_T is record

PARITY: std_ulogic;

ADDR: std_ulogic_vector(3 downto 0);

DEST: std_ulogic_vector(3 downto 0);

end record;

```

```

typedef struct {

logic     PARITY;

logic[3:0] ADDR;

logic[3:0] DEST;

} pkt_t;

```

```

signal MYPKT : PKT_T;

...

MYPKT.ADDR <= "1100";</pre>

```

```

pkt_t mypkt;

...

mypkt.ADDR = 12;

```

```

31 3 0

```

PARITY ADDR DEST The mypkt structure/ record is "unpacked"

In SystemVerilog, struct variables can also be declared directly, without the typedef

Structure definitions are just like in C but without the optional structure tag before the '{'

```

struct {

bit [7:0] opcode;

bit [23:0] addr;

} IR;

```

no typedef

#### Packed Structures and Unions

```

typedef struct packed {

logic [15:0] source_port;

logic [15:0] dest_port;

logic [31:0] sequence;

} tcp_t;

typedef struct packed {

logic [15:0] source_port;

logic [15:0] dest_port;

logic [15:0] length;

logic [15:0] checksum

} udp_t;

```

```

typedef union packed {

tcp_t tcp_h;

udp_t udp_h;

bit [63:0] bits;

bit [7:0][7:0] bytes;

} ip_t;

All

members

of a union

must

be the

same size

```

```

tcp_t source_port dest_port sequence

udp_t source_port dest_port length checksum

```

Create multiple layouts for accessing data VHDL records not explicitly packed

Operate on entire structure as a whole

### **Type Conversion**

```

Unpacked Structure

typedef struct

PARITY;

logic

logic[3:0] ADDR;

User-defined type:

logic[3:0] DEST;

packed bit vector

} pkt t;

typedef bit[8:0] vec t;

pkt_t mypkt;

vec t myvec;

Cast mypkt as type vec_t

myvec = vec_t'(mypkt);

mypkt = pkt t'(myvec);

Cast myvec as type pkt_t

```

User-defined types and explicit casting improve readability and modularity

Similar to Qualified Expressions or conversion functions in VHDL

#### **Data Organization - Enum**

#### VHDL:

```

type FSM ST is

{IDLE,

INIT,

DECODE,

...};

signal pstate, nstate : FSM_ST;

case (pstate) is

when idle:

if (sync = '1') then

nstate <= init;</pre>

end if;

when init:

if (rdy = '1') then

nstate = decode;

end if;

end case;

```

#### SystemVerilog:

```

typedef enum logic [2:0]

{idle = 0,}

init = 3,

decode, // = 4

...} fsmstate;

fsmstate pstate, nstate;

case (pstate)

idle: if (sync)

nstate = init;

init: if (rdy)

nstate = decode;

endcase

```

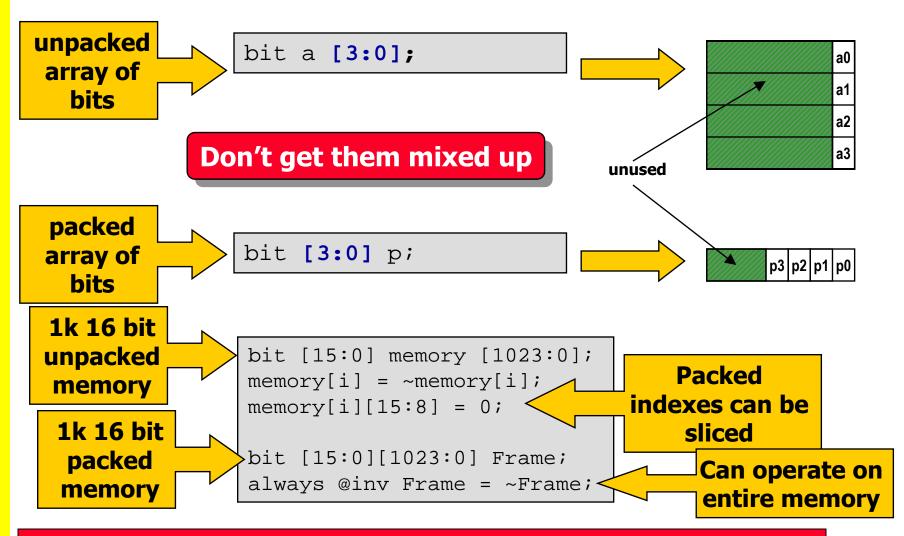

## Packed and Unpacked Arrays

SystemVerilog also includes the VHDL-like array attribute functions: \$left, \$right, \$low, \$high, \$increment, \$length and \$dimensions

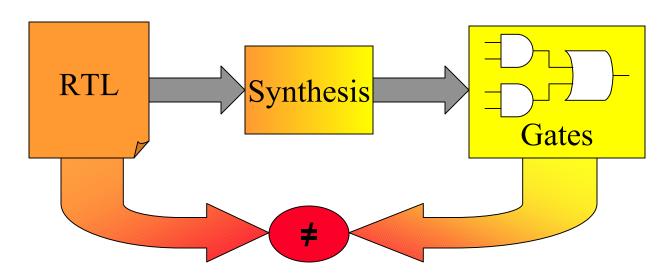

## **Pre-Post Synthesis Mismatches**

- Causes

- Sensitivity list mismatches

- Pragmas affect synthesis but not simulation

- SystemVerilog Solves these problems

- Specialized always blocks automate sensitivity

- Synthesis directives built into the language

#### Design Intent – always\_{comb,latch,ff}

- always blocks do not guarantee capture of intent

- If not edge-sensitive then only a warning if latch inferred

- always\_comb, always\_latch and always\_ff are explicit

- Compiler Now Knows User Intent and can flag errors accordingly

```

//OOPS forgot Else but it's

//only a synthesis warning

always @(a or b)

if (b) c = a;

//Compiler now asks

//"Where's the else?"

always comb

if (b) c = a;

//Intent: Conditional

// Assignment

always latch

if (clk)

if (en) Q <= d;

//Conversely unconditionally

//assigned -is it a latch?

always latch

q <=d

```

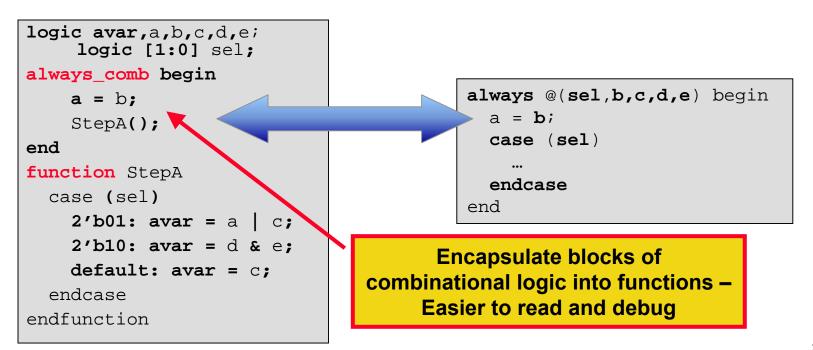

## always\_comb Sensitivity

- always\_comb eliminates sensitivity list issues

- Ensures synthesis-compatible sensitivity

- Helps reduce "spaghetti code"

- Consider that always\_comb derives sensitivity from

- RHS/expr in process

- RHS/expr of statements in Function Calls

## **Design Intent – Unique/Priority**

- Parallel\_case/full\_case pragmas affect synthesis behavior but not simulation behavior

- Unique keyword means that one and only one branch will be taken (same as full\_case parallel\_case)

- Priority keyword means that the first branch will be taken (same as full\_case)

- Will cause simulation run-time error if illegal value is seen

```

unique if (sel==3'b001)

unique case (sel)

sel must be

sel[0] : muxo = a;

muxo = ai

"one-hot"

sel[1] : muxo = b;

else if (sel == 3'b010)

muxo = bi

sel[2] : muxo = c;

No ending

No default

else if (sel == 3'b100)

endcase

else needed

clause needed

muxo = c;

priority case (1'b1)

priority if (irq0)

irq0 has

irq0: irq = 4'b1 << 0;

irq = 4'b1;

highest

else if (irq1)

irq1: irq = 4'b1 << 1;

priority

irq2: irq = 4'b1 << 2;

irq = 4'b2;

irq3: irq = 4'b1 << 3;

else if (irq2)

endcase

irq = 4'b4;

```

## Syntax – Implicit Named Port

- Creating netlists by hand is tedious

- Generated netlists are unreadable

- Many signals in instantiations

- Instantiations cumbersome to manage

- Implicit port connections dramatically improve readability

- Use same signal names up and down hierarchy where possible

- Port Renaming Accentuated

- .name allows explicit connections with less typing (and less chance for error)

```

module top();

logic rd,wr;

tri [31:0] dbus,abus;

tb(.*);

dut(.*);

endmodule

```

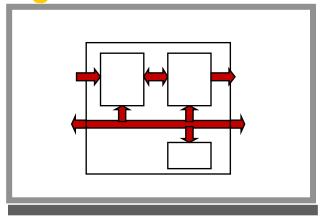

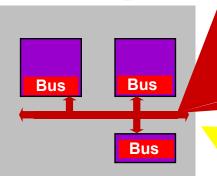

#### SystemVerilog Interfaces

#### **Design On A White Board**

SystemVerilog Design

**Interface Bus**

Signal 1 Signal 2 Read() Write()

**Assert**

**HDL Design**

**Complex signals**

Bus protocol repeated in blocks

Hard to add signal through hierarchy

#### Communication encapsulated in interface

- Reduces errors, easier to modify

- Significant code reduction saves time

- Enables efficient transaction modeling

- Allows automated block verification

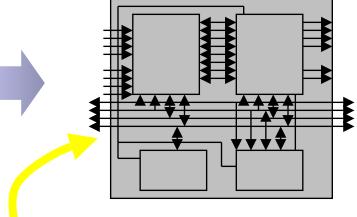

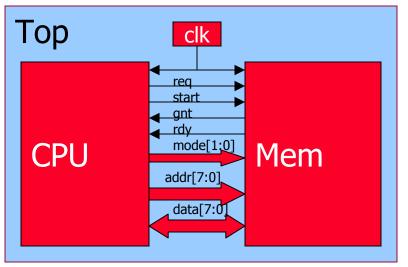

#### **Example without Interface**

```

entity memMod is

port(req,clk,start : in bit;

mode: in std logic vector(1 downto 0);

addr : in std logic vector(7 downto 0);

data : inout std logic vector(7 downto 0);

qnt, rdy : out bit);

end memMod;

architecture RTL of memMod is

process (clk) begin

wait until clk'event and clk='1';

qnt <= req AND avail;</pre>

end architecture RTL;

entity cpuMod is

port(clk, gnt, rdy : in bit;

data : inout std_logic_vector(7 downto 0);

req, start : out bit;

mode : out std_logic_vector(1 downto 0);

addr : out std logic vector(7 downto 0));

end cpuMod;

architecture RTL of cpuMod is

end architecture RTL;

```

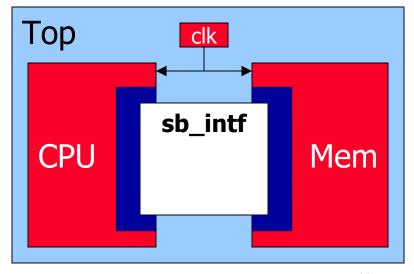

#### **Example Using Interfaces**

```

interface simple bus;

logic req, qnt;

Bundle

logic [7:0] addr,data;

signals in

logic [1:0] mode;

interface

logic start,rdy;

endinterface: simple bus

Use interface

keyword in port list

module memMod(interface a,

input bit clk);

logic avail;

always @(posedge clk)

a.gnt <= a.req & avail;

endmodule

Refer to intf

signals

module cpuMod(interface b,

input bit clk);

endmodule

```

```

module top;

bit clk = 0;

simple_bus sb_intf;

interface instance

memMod mem(sb_intf, clk);

cpuMod cpu(.b(sb_intf),

.clk(clk))

endmodule

Connect

interface

```

### **Using Different Interfaces**

```

typedef logic [31:0]

data_type;

bit clk;

always #100 clk = !clk;

parallel channel(clk);

send s(clk, channel);

receive r(clk, channel);

```

```

typedef logic [31:0]

data_type;

bit clk;

always #100 clk = !clk;

serial channel(clk);

send s(clk, channel);

receive r(clk, channel);

```

```

send receive

serial

```

Simplifies design exploration Extends block-based design to the communication between blocks

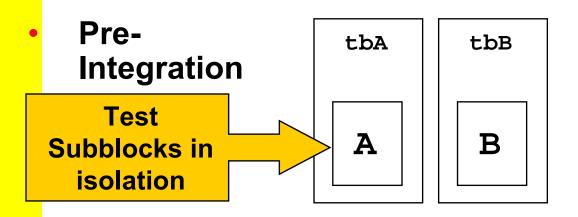

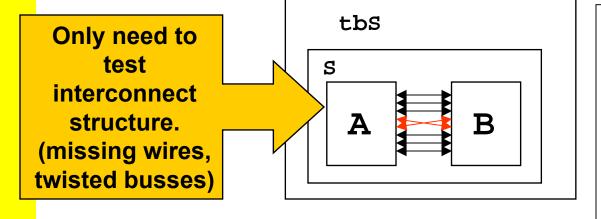

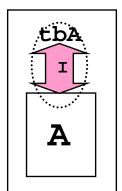

#### **Conventional Verification**

- Testbench reuse problems

- tbA and tbB separate

- Complex interconnect

- Hard to create tests to check all signals

- Slow, runs whole design even if only structure is tested

Post-Integration

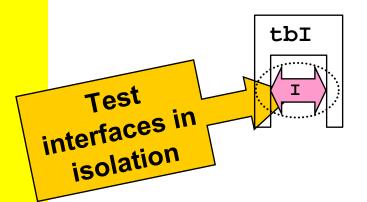

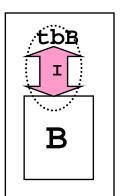

## SystemVerilog Verification

Pre-Integration

Post-Integration

- Interfaces provide reusable components

- tbA and tbB are 'linked'

- Interface is executable spec

- Wiring up is simple and not error prone

- Interfaces can contain protocol checkers and coverage counters

- Start Chip-Level Verification at the Block Level

#### **Operator Overloading**

- Enable use of simple operators with Complex SV Types struct3 = struct1 + struct2

- Operator Overloading is allowed for type combinations not already defined by SV Syntax

```

bind overload_operator function data_type

function_identifier (overload_proto_formals)

```

```

typedef struct {

bit sign;

bit [3:0] exponent;

bit [10:0] mantissa;

} float;

bind + function float faddfr(float, real);

bind + function float faddff(float, float);

float A, B, C, D;

assign A = B + C; //equivalent to A = faddff(B, C);

assign D = A + 1.0; //equivalent to A = faddfr(A, 1.0);

```

# Packages and Separate Compilation

- Allows sharing of:

- nets, variables, types,

- tasks, functions

- classes, extern constraints, extern methods

- parameters, localparams, spec params

- properties, sequences

- Allows unambiguous references to shared declarations

- Built-in functions and types included in std package

- Groups of files can now be compiled separately

```

package ComplexPkg;

typedef struct {

float i, r;

} Complex;

function Complex add(Complex a, b)

add.r = a.r + b.r;

add.i = a.i + b.i;

endfunction

function Complex mul(Complex a, b)

mul.r = (a.r * b.r) + (a.i * b.i);

mul.i = (a.r * b.i) + (a.i * b.r);

endfunction

endpackage : ComplexPkq

module foo (input bit clk);

import ComplexPkg::*

Complex a,b;

always @(posedge clk)

c = add(a,b);

endmodule

```

#### Agenda

- Introduction

- SystemVerilog Design Features

- SystemVerilog Assertions

- SystemVerilog Verification Features

- Using SystemVerilog and VHDL Together

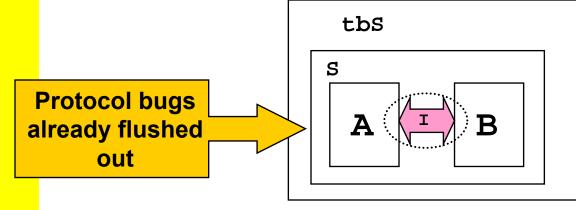

#### What is an Assertion?

A concise description of [un]desired behavior

"After the request signal is asserted, the acknowledge signal must come 1 to 3 cycles later"

## Concise and Expressive SVA

#### **SVA** Assertion

**HDL** Assertion

```

property req_ack;

@(posedge clk) req ##[1:3] $rose(ack);

endproperty

as_req_ack: assert property (req_ack);

```

```

0 1 2 3 4 5

req

ack

Example intended behavior

```

```

sample_inputs : process (clk)

VHDL

begin

if rising edge(clk) then

STROBE REQ <= REQ;

STROBE ACK <= ACK;

end if;

end process;

protocol: process

variable CYCLE CNT : Natural;

begin

wait until rising edge(CLK);

exit when (STROBE_REQ = '0') and (REQ = '1');

end loop;

CYCLE CNT := 0;

1000

wait until rising edge(CLK);

CYCLE CNT := CYCLE_CNT + 1;

exit when ((STROBE ACK = '0') and (ACK = '1')) or (CYCLE CNT = 3);

end loop;

if ((STROBE ACK = '0') and (ACK = '1')) then

report "Assertion success" severity Note;

report "Assertion failure" severity Error;

end if:

end process protocol;

```

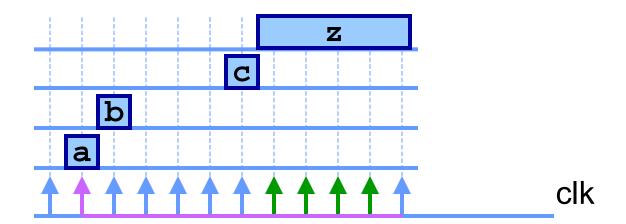

#### Sequential Regular Expressions

- Describing a sequence of events

- Sequences of Boolean expressions can be described with a specified time step in-between

```

<mark>@</mark>(posedge clk) a ##1 b ##4 c ##[1:5] z;

```

#### **Property Definition**

- **Property Declaration:** property

- Declares property by name

- Formal parameters to enable property reuse

- Top Level Operators

#### **Assertion Directives**

- assert checks that the property is never violated

- cover tracks all occurrences of property

# Manipulating Data: Local Dynamic Variables

- Declared Locally within Sequence/Property

- New copy of variable for each sequence invocation

- Assigned anywhere in the sequence

- Value of assigned variable remains stable until reassigned in a sequence

#### **Local Dynamic Variable Example**

```

property e;

int x;

(valid,(x=in))|=> ##5(out==(x+1));

endproperty

```

# **Embedding Concurrent Assertions**

```

property s1;

(req && !gnt)[*0:5] ##1 gnt && req ##1 !req;

endproperty

Automatically Updates

always @(posedge clk or negedge reset)

Enabling Condition as

if(reset == 0) do_reset;

Design Changes

else if (mode == 1)

Infers clock from

case(st)

instantiation

REQ: if (!arb)

if (foo)

Requires User to Update

st <= REQ2;

Manually as Design

PA: assert property (s1);

Changes

property p1;

@(posedge clk) ((reset == 1) && (mode == 1)

&& (st == REQ) && (!arb) && (foo)) => s1;

endproperty

DA: assert property (p1);

```

#### **Bind statement**

bind module\_or\_instance\_name instantiation;

```

module/instance name

Top

cpu1

bind cpu cpu_props cpu_rules1(a,b,c);

module cpu(a,b);

reg c;

instance name

endmodule

program name

cpu2

program cpu_props(input d,e,f);

module cpu(a,b);

assert property (d ##1 e |=> f[*3]);

reg c;

endprogram

endmodule

Equivalent to:

assert property (top.cpu1.a ##1 top.cpu1.b |=> top.cpu1.c[*3]);

assert property (top.cpu2.a ##1 top.cpu2.b |=> top.cpu2.c[*3]);

or

cpu_props cpu_rules1(a,b,c); // in module cpu

```

Bind assertions to VHDL code

## Flexible Assertions Use-Model

#### Design Engineers

- Able to define assertions in-line with design code

- Assertions typically cover implementation-level detail

- Capture assumptions while they're fresh in the designer's mind

- Verification Engineers

- Able to define assertions external to RTL code and "bind" them to the design

- Assertions typically cover interface/system behavior

- Do not need to modify the golden RTL to add assertions

# Agenda

- Introduction

- SystemVerilog Design Features

- SystemVerilog Assertions

- SystemVerilog Verification Features

- Using SystemVerilog and VHDL Together

# **Dynamic Arrays**

```

Declaration syntax

<type> <identifier> [ ];

bit[3:0] dyn[];—

Initialization syntax

<array> = new[<size>];

dyn

dyn = new[4];

Equivalent to:

bit[3:0] dyn[0:3];

Size method

function int size();

int j = dyn.size; //j=4

Resize syntax

dyn = new[j * 2];

Equivalent to:

bit[3:0] dyn[0:7];

```

# **Associative Arrays**

- Sparse Storage

- Elements Not Allocated Until Used

- Index Can Be of Any Packed Type, String or Class

#### **Declaration syntax**

```

<type> <identifier> [<index_type>];

<type> <identifier> [*]; // "arbitrary" type

```

#### **Example**

```

struct packed {int a; logic[7:0] b} mystruct;

int myArr [mystruct]; //Assoc array indexed by mystruct

```

#### **Built-in Methods**

```

num(), delete([index]), exists(index);

first/last/prev/next(ref index);

```

**Ideal for Dealing with Sparse Data**

#### Queues

- Variable-sized Array: data\_type name [\$]

- Uses array syntax and operators

```

int q[$] = { 2, 4, 8 }; int e, pos, p[$];

e = q[0];    // read the first (leftmost) item

e = q[$];    // read the last (rightmost) item

q = { q, 6 };    // append: insert '6' at the end

q = { e, q };    // insert 'e' at the beginning

q = q[1:$];    // delete the first (leftmost) item

q = q[1:$-1];    // delete the first and last items

```

- Synthesizable if maximum size is known

- q[\$:25] // maximum size is 25

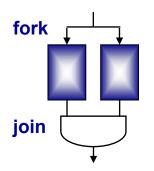

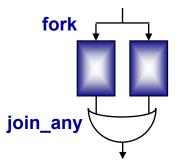

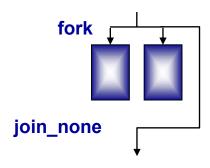

# **Dynamic Processes and Threads**

SystemVerilog adds dynamic parallel processes using fork/join\_any and fork/join\_none

- Threads created via fork...join

- Threads execute until a blocking statement

- wait for: (event, mailbox, semaphore, variable, etc.)

- disable fork to terminate child processes

- wait\_child to wait until child processes complete

- Built-in process object for fine-grain control

Multiple Independent Threads Maximize Stimulus Interactions

# Inter-Process Synchronization

#### Events

- Events are variables can be copied, passed to tasks, etc.

- event.triggered; // persists throughout timeslice, avoids races

- wait\_order(), wait\_any(), wait\_all(<events>);

- Semaphore Built-in Class

```

semaphore semID = new(1);

semID.get(1);

semID.put(1);

```

- Mailbox Built-in Class

- Arbitrary type

```

mailbox #(type) mbID = new(5);

mbID.get(msg);

mbID.put(msg);

```

Ensures meaningful, race-free communication between processes

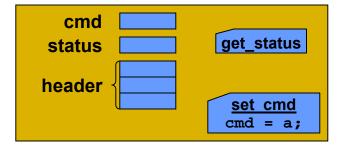

### Class Definition

#### **Definition syntax**

```

class name;

<data_declarations>;

<task/func_decls>;

endclass

```

extern keyword allows for out-of-body method declaration

"::" operator links method declaration to Class definition

```

class Packet;

bit[3:0] cmd;

int status;

myStruct header;

function int get_status();

return(status);

endfunction

extern task set_cmd(input bit[3:0] a);

endclass

```

```

task Packet::set_cmd(input bit[3:0] a);

cmd = a;

endtask

```

Note: Class declaration does not allocate any storage

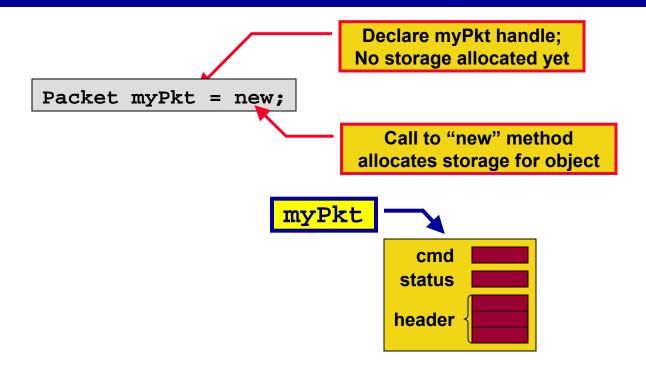

### **Class Instantiation**

- User may override default "new" method

- Assign values, call functions, etc.

- User-defined new method may take arguments

- Garbage Collection happens automatically

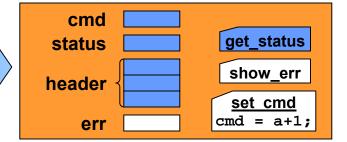

#### Class Inheritance

## Keyword extends Denotes Hierarchy of Class Definitions

- Subclass inherits properties, constraints and methods from parent

- Subclass can redefine methods explicitly

```

class ErrPkt extends Packet;

bit[3:0] err;

function bit[3:0] show_err();

return(err);

endfunction

task set_cmd(input bit[3:0] a);

cmd = a+1;

endtask // overrides Packet::set_cmd

endclass

```

#### Packet:

#### ErrPkt:

Allows Customization Without Breaking or Rewriting Known-Good Functionality in the Base Class

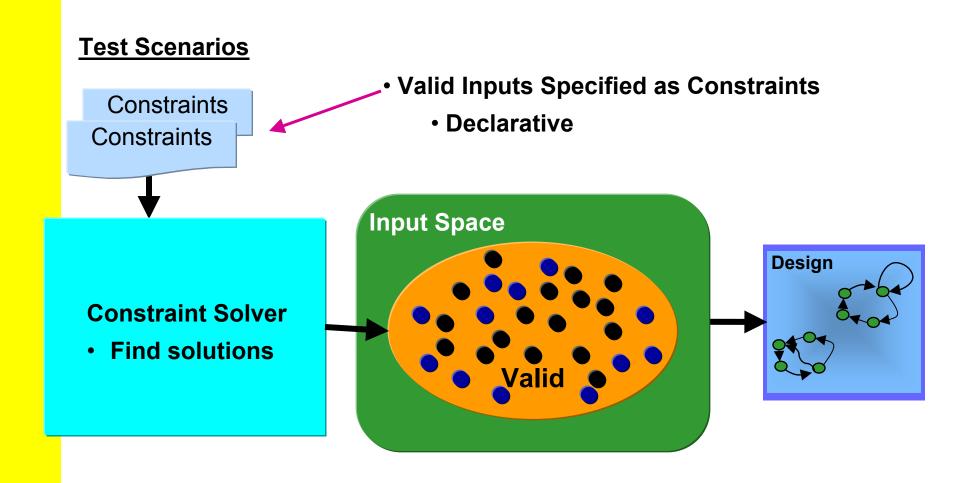

## **Constrained Random Simulation**

**Exercise Hard-to-Find Corner Cases While Guaranteeing Valid Stimulus**

### **Basic Constraints**

Constraints are Declarative

```

class Bus;

rand bit[15:0] addr;

rand bit[31:0] data;

randc bit[3:0] mode;

constraint word_align {addr[1:0] == 2'b0;}

endclass

```

- Calling randomize selects values for all random variables in an object such that all constraints are satisfied

- Generate 50 random data and word\_aligned addr values

```

Bus bus = new;

repeat (50)

if ( bus.randomize() == 1 ) // 1=success,0=failure

$display ("addr = %16h data = %h\n", bus.addr,

bus.data);

else

$display ("Randomization failed.\n");

```

#### **In-Line Constraints**

#### **Additional Constraints In-line Via**

obj.randomize()with <constraint\_blk>

```

task exerBus(MyBus m);

int r;

r = m.randomize() with {type==small};

endtask

Force type

to be small

```

In-Line Constraints Pick Up Variables From the Object

# **Layered Constraints**

- Constraints Inherited via Class Extension

- Just like data and methods, constraints can be inherited or overridden

```

typedef enum { low, high, other } AddrType ;

class MyBus extends Bus;

rand AddrType type;

constraint addr_rang {

( type == low ) => addr in { [ 0 : 15] };

( type == high ) => addr in { [128 : 255] }; }

endclass

```

- Bus::word\_align Constraint is also active

- Inheritance allows layered constraints

- Constraints can be enabled/disabled via constraint\_mode() method

Allows Reusable Objects to be Extended and/or Constrained to Perform Specific Functions

# Weighted Random Case

- Randomly select one statement

- Label expressions specify distribution weight

- If a == 4:

- -branch 1 taken with 3/8 probability (37.5%)

- -branch 2 taken with 1/8 probability (12.5%)

- -branch 3 taken with 4/8 probability (50.0%)

# Scope Randomization & Constraint Checking

randomize method can be applied to any variable

```

[std::] randomize ( [ variable_list ] ) [ with { constraint_block } ]

module stim;

bit[15:0] a;

bit[31:0] b;

function bit gen_stim();

bit success, rd_wr;

success = randomize( a, b, rd_wr ) with { a > b };

return rd_wr;

endfunction

...

endmodule

```

#### Constraints can be checked in-line

```

status = class_obj.randomize(null);

Passing "null" argument to randomize

checks the constraints

0 = valid, 1 = invalid

```

# Functional Coverage

- New covergroup container allows declaration of

- coverage points

- -variables

- -expressions

- -transitions

- cross coverage

- sampling expression: clocking event

```

enum { red, green, blue } color; Sample event

bit [3:0] pixel_adr;

covergroup g1 @(posedge clk); 3 bins for color

c: coverpoint color;

a: coverpoint pixel_adr;

AxC: cross color, pixel_adr;

endgroup;

6 bins for pixel

6 bins for pixel

7 cross products

```

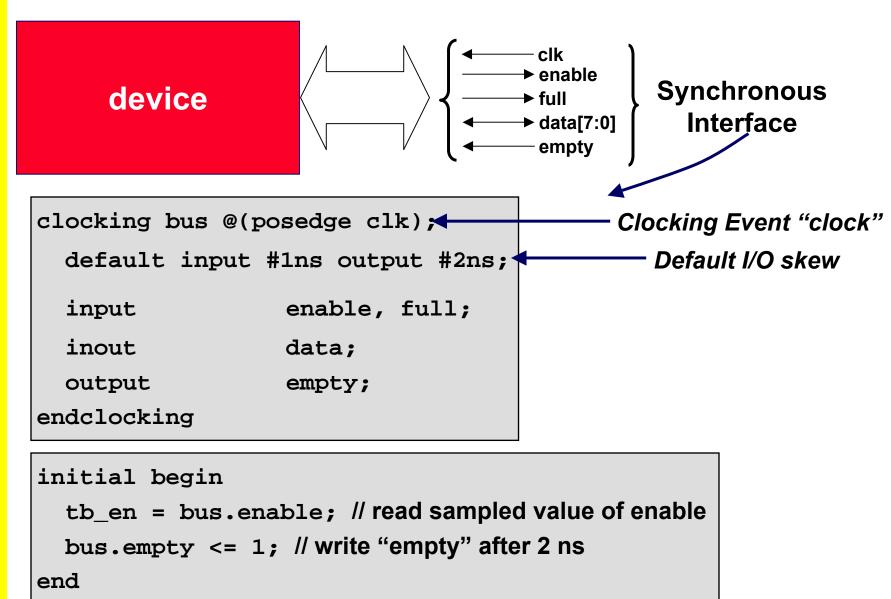

## Synchronous Interfaces: Clocking

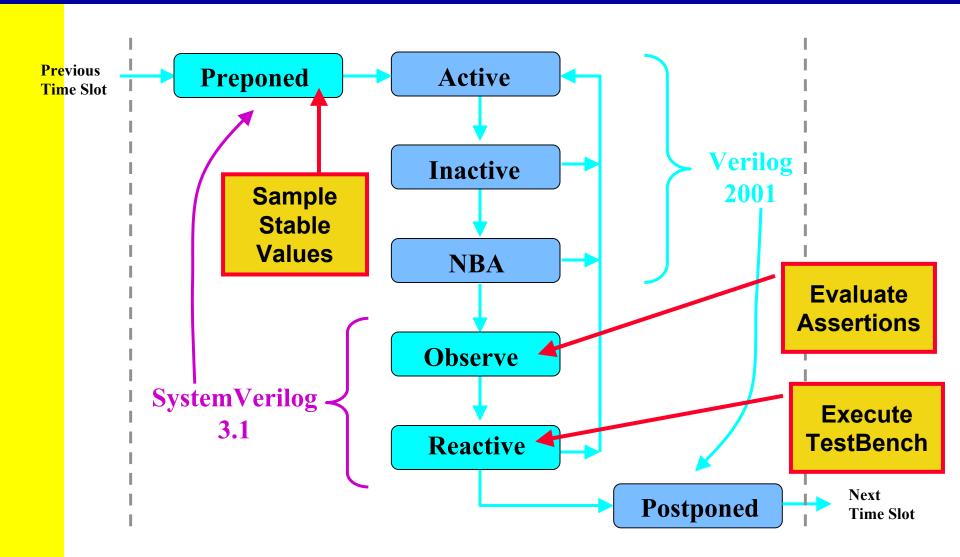

# **Program Block**

- Purpose: Identifies verification code

- A program differs from a module

- Only initial blocks allowed

- Special semantics

- Executes in Reactive region

design → clocking/assertions → program

- Program block variables cannot be modified by the design

The Program block functions pretty much like a C program Testbenches are more like software than hardware

# **TB + Assertions Example**

A new bus cycle may not start for 2 clock cycles after an abort cycle has completed

```

sequence abort cycle;

!rdy throughout (as ##1 ds[*1:$] ##1 abort);

endsequence

cover property (@(posedge clk) abort cycle)

wait cnt = 2;

property wait_after_abort;

@(posedge clk) abort_cycle |=> !as[*2];

endproperty

assert property (wait after abort);

program manual stimulus generator;

Simulation Monitors

repeat(1000) begin

and Constraints

generate transaction(addr,data);

while(wait cnt > 0)

for Formal

@(posedge clk) wait cnt--;

Analysis

end

endprogram

```

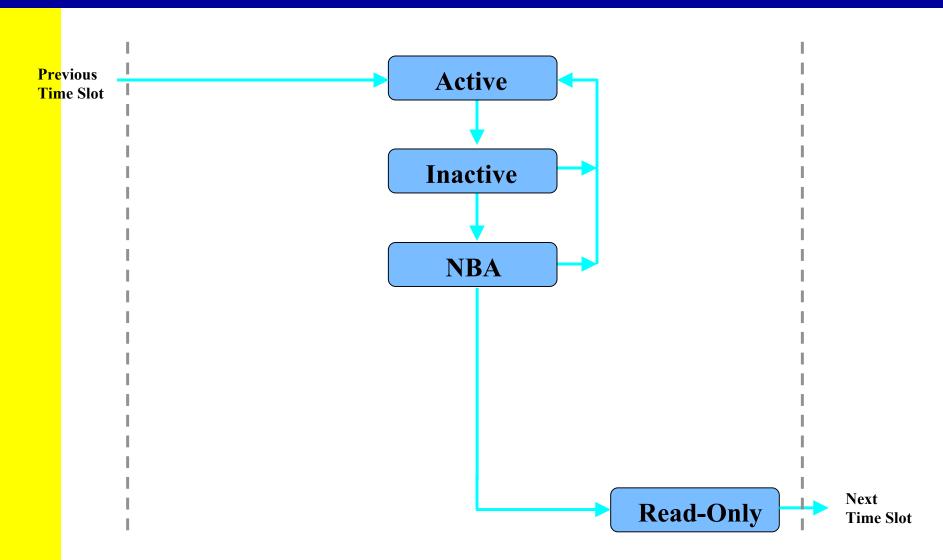

# SystemVerilog Enhanced Scheduling

# SystemVerilog Enhanced Scheduling

# Agenda

- Introduction

- SystemVerilog Design Features

- SystemVerilog Assertions

- SystemVerilog Verification Features

- Using SystemVerilog and VHDL Together

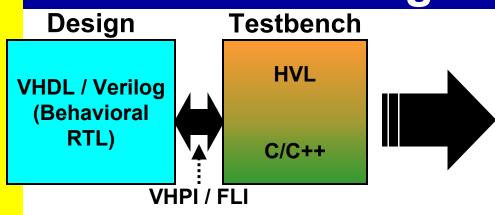

# SystemVerilog With VHDL

- Verilog-VHDL Interface limited to net/vector types

- VHDL records and arrays packed into bit vectors

- SystemVerilog supports higher-level data types

- Synthesizable types are synthesizable across the interface

| VHDL          | SystemVerilog |

|---------------|---------------|

| Record        | Struct        |

| Array         | Array         |

| Multi-D Array | Multi-D Array |

| Enum          | Enum          |

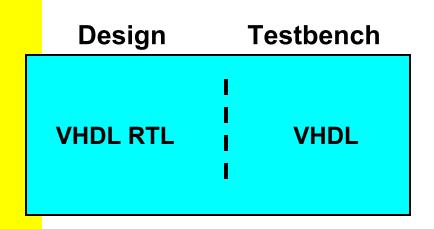

### **Pure VHDL Simulation Flow**

- + Single language (VHDL) for design and testbench

- No constrained random TB

- No temporal assertions

- No functional coverage

- Coherent environment for design and verification

- Limited testbench capabilities in VHDL "promote" a directed test based verification methodology

- Lack of constrained random / assertion / coverage ->

low "bug-finding effectiveness"

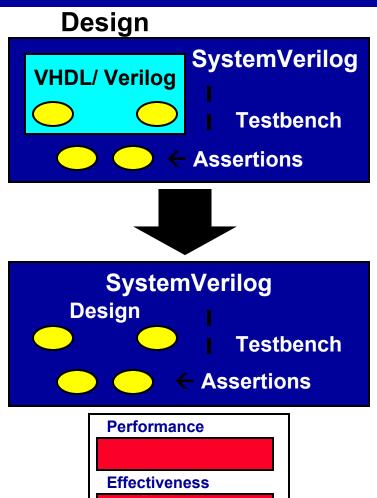

# SystemVerilog is Evolutionary for VHDL and Verilog Users

- Increases productivity for Design and Verification

- Concise coding constructs

- Rich assertions

- Complete testbench

- Constrained Random Data

- Functional Coverage

# The Importance of a Single Language

#### Unified Scheduling

- Basic Verilog

- won't work

- Ensures Pre/Post-Synth Consistency

- Enables

- **Performance**

- **Optimizations**

# Knowledge of Other Language Features

- Testbench and Assertions

- Interfaces and

- **Classes**

- Sequences and Events

#### Reuse of Syntax/Concepts

- Sampling for assertions and clocking domains

- Method syntax

- Queues use common concat/array operations

- Constraints in classes and procedural code

## SystemVerilog Benefits for VHDL Users

- Many VHDL modeling features are in SystemVerilog

- Don't have to give up high-level data types

- Some features (enums) extended beyond VHDL capabilities

- Mixed-HDL environments are a reality

- Higher-level data types supported across boundary

- Continue to use VHDL legacy blocks

- Easier to adopt SystemVerilog incrementally

- Industry-Standard Verification Language works with VHDL designs

- Constrained random data generation

- Object-oriented

- Assertions

- SystemVerilog supports Design for Verification

- Interfaces and assertions capture design intent

- Efficient and intuitive interactions between testbench and assertions

## **Evolution of Verification Productivity**